### MEMS audio sensor: digital microphone with multiple performance modes

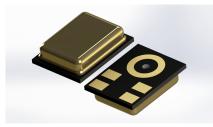

RHLGA 5LD (3.5 x 2.65 x 0.98 mm)

#### **Product status link**

MP23DB01HP

| Product summary     |                                     |  |  |

|---------------------|-------------------------------------|--|--|

| Order code          | MP23DB01HPTR                        |  |  |

| Temp. range<br>[°C] | -40 to +85                          |  |  |

| Package             | RHLGA 5LD<br>(3.5 x 2.65 x 0.98) mm |  |  |

| Packing             | Tape and reel                       |  |  |

#### **Features**

- Omnidirectional digital microphone

- Very low distortion / very high AOP

- 135 dBSPL acoustic overload point for all operative modes

- Sensitivity: –41 dBFS ±1dB

- Sensitivity matching

- "Always-on" experience with low power consumption

- Multiple performance modes (sleep, low-power, performance)

- · Typical current consumption

- 2 μA (sleep mode)

- 285 μA (low-power mode)

- 800 μA (performance mode)

- · PDM single-bit output with option for stereo configuration

- RHLGA package

- Bottom-port design

- SMD-compliant

- EMI-shielded

- ECOPACK, RoHS and "Green" compliant

### **Applications**

- Smart IoT

- · Smartphones and handsets

- · Smart speakers

- · Laptops and notebook computers

- Wearable devices

- TWS and headsets

- Hands-free calling

### **Description**

The MP23DB01HP is an ultra-compact, low-power, omnidirectional, digital MEMS microphone built with a capacitive sensing element and an IC interface with optional stereo configuration.

The sensing element, capable of detecting acoustic waves, is manufactured using a specialized silicon micromachining process dedicated to producing audio sensors.

The IC interface is manufactured using a CMOS process that allows designing a dedicated circuit able to provide a digital signal externally in PDM format.

The MP23DB01HP offers multiple performance modes (power-down, low-power and performance mode) enabled by different clock frequency ranges. The device has a very high AOP in performance mode, sensitivity range of  $\pm 1$  dB and high SNR for all operative modes.

The MP23DB01HP is available in a bottom-port, SMD-compliant, EMI-shielded package and is guaranteed to operate over an extended temperature range from -40 °C to +85 °C.

## 1 Pin description

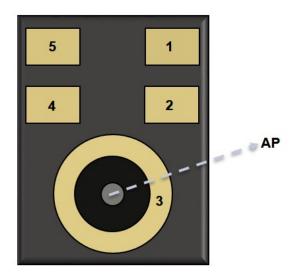

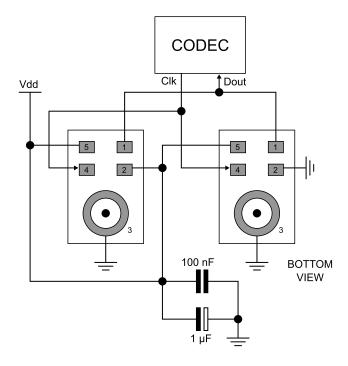

Figure 1. Pin connections

# **Bottom View**

Table 1. Pin description

| Pin #           | Pin name | Function                     |

|-----------------|----------|------------------------------|

| 1               | DOUT     | Left/right PDM data output   |

| 2               | L/R      | Left/right channel selection |

| 3 (ground ring) | GND      | 0 V supply                   |

| 4               | CLK      | Synchronization input clock  |

| 5               | VDD      | Supply voltage               |

DS13336 - Rev 4 page 2/15

## 2 Acoustic and electrical specifications

### 2.1 Acoustic and electrical characteristics

The values listed in the table below are specified for Vdd = 1.8 V, clock = 2.4 MHz, T =  $25 \,^{\circ}\text{C}$ , no load, unless otherwise noted.

Table 2. Acoustic and electrical characteristics

| Symbol           | Parameter                                             | Test condition      | Min.     | Typ. <sup>(1)</sup> | Max.     | Unit |

|------------------|-------------------------------------------------------|---------------------|----------|---------------------|----------|------|

| Vdd              | Supply voltage                                        |                     | 1.6      |                     | 3.6      | V    |

|                  |                                                       | Power-down mode     | 0        |                     | 0.15     |      |

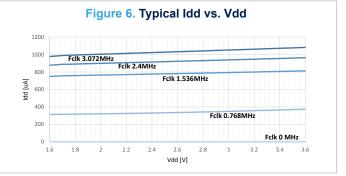

| $f_{CLK}$        | Clock frequency range <sup>(2)(3)</sup>               | Low-power mode      | 0.54     | 0.768               | 1.1      | MHz  |

|                  |                                                       | Performance mode    | 1.5      | 2.4                 | 3.3      |      |

|                  | Current consumption in low-power mode                 | Fc = 768 kHz        |          | 285                 |          |      |

| ldd              | Current consumption in performance mode               | Fc = 2.4 MHz        |          | 800                 |          | μА   |

|                  |                                                       | Fc = 3.072 MHz      |          | 880                 |          |      |

| IddPdn           | Current consumption in power-down mode <sup>(4)</sup> |                     |          | 2                   | 5        |      |

| Icc              | Short-circuit current                                 |                     | 1        |                     | 10       | mA   |

| V <sub>IOL</sub> | Low-level logic input/output voltage                  | lout = 1 mA         | -0.3     |                     | 0.35xVdd | V    |

| V <sub>IOH</sub> | High-level logic input/output voltage                 | lout = 1 mA         | 0.65xVdd |                     | Vdd+0.3  | V    |

| TWK              | Wake-up time <sup>(5)</sup>                           | Specified by design |          |                     | 20       | ms   |

| Roll-off         | Frequency response                                    | at -3 dB            |          | 35                  |          | Hz   |

| Cload            | DOUT load capacitance                                 |                     |          |                     | 100      | pF   |

| Тор              | Operating temperature range                           |                     | -40      |                     | +85      | °C   |

<sup>1.</sup> Typical specifications are not guaranteed.

5. Time from the first clock edge to valid output data

DS13336 - Rev 4 page 3/15

<sup>2.</sup> Duty cycle: min = 40% max = 60%

In case of mode change (from low-power to performance mode or vice versa), the clock has to be continuous or has to be stopped for at least 50 μs.

<sup>4.</sup> Input clock in static mode

The values listed in the table below are specified for Vdd = 1.8 V, clock = 768 kHz, no load, T =  $25 ^{\circ}\text{C}$ , unless otherwise noted.

Table 3. Low-power mode

| Symbol | Parameter                 | Test condition                                 | Min. | Typ. <sup>(1)</sup> | Max. | Unit  |

|--------|---------------------------|------------------------------------------------|------|---------------------|------|-------|

| ldd    | Current consumption       |                                                |      | 285                 |      | μΑ    |

| So     | Sensitivity               | 94 dBSPL @ 1 kHz                               | -25  | -24                 | -23  | dBFS  |

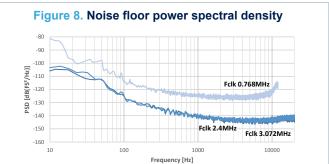

| SNR    | Signal-to-noise ratio     | 94 dBSPL @ 1 kHz<br>A-weighted (20 Hz - 8 kHz) |      | 64                  |      | dB(A) |

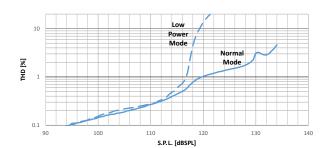

| THD    | Total harmonic distortion | 94 dBSPL @ 1 kHz                               |      | 0.2                 |      | %     |

| AOP    | Acoustic overload point   |                                                |      | 120                 |      | dBSPL |

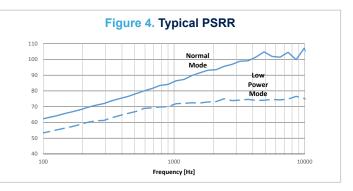

| PSR    | Power supply rejection    | 100 mVpp sinewave @ 217 Hz                     |      | -85                 |      | dBFS  |

<sup>1.</sup> Typical specifications are not guaranteed.

The values listed in the table below are specified for Vdd = 1.8 V, clock = 2.4 MHz, no load, T = 25 °C, unless otherwise noted.

Table 4. Performance mode

| Symbol | Parameter                                       | Test condition             | Min. | Typ. <sup>(1)</sup> | Max. | Unit  |

|--------|-------------------------------------------------|----------------------------|------|---------------------|------|-------|

| Idd    | Current consumption                             | 2.4 MHz                    |      | 800                 |      |       |

| luu    | Current consumption                             | 3.072 MHz                  |      | 880                 |      | μА    |

| So     | Sensitivity                                     | 94 dBSPL @ 1 kHz           | -42  | -41                 | -40  | dBFS  |

|        | Signal-to-noise ratio                           | 2.4 MHz                    |      | 65                  |      |       |

| SNR    | 94 dBSPL @ 1 kHz<br>A-weighted (20 Hz - 20 kHz) | 3.072 MHz                  |      | 65.5                |      | dB(A) |

| THD    | Total harmonic distortion                       | 94 dBSPL @ 1 kHz           |      | 0.2                 |      | %     |

| IIID   | Total Harmonic distortion                       | 110 dBSPL @ 1 kHz          |      | 0.5                 |      | 70    |

| AOP    | Acoustic overload point                         |                            |      | 135                 |      | dBSPL |

| PSR    | Power supply rejection                          | 100 mVpp sinewave @ 217 Hz |      | -95                 |      | dBFS  |

<sup>1.</sup> Typical specifications are not guaranteed.

DS13336 - Rev 4 page 4/15

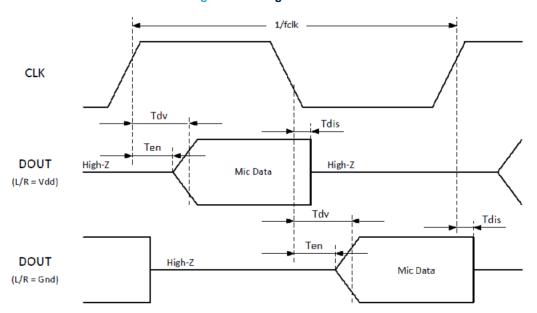

## 2.2 Timing characteristics

**Table 5. Timing characteristics**

| Symbol           | Description                               | Min. | Max. | Unit |

|------------------|-------------------------------------------|------|------|------|

| T <sub>dv</sub>  | Delay time to valid data (Cload = 100 pF) |      | 120  | ns   |

| T <sub>en</sub>  | Delay time to driven data                 | 19   |      | ns   |

| T <sub>dis</sub> | Delay time to high-Z                      | 4    | 17   | ns   |

Figure 2. Timing waveforms

DS13336 - Rev 4 page 5/15

### 2.3 Typical performance curves

Figure 5. Typical THD at 1 kHz vs. sound pressure level

Figure 7. Typical THD at 1 kHz vs. sound pressure level

DS13336 - Rev 4 page 6/15

## 3 Absolute maximum ratings

Stresses above those listed as "Absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 6. Absolute maximum ratings

| Symbol             | Ratings                                                          | Maximum value    | Unit |

|--------------------|------------------------------------------------------------------|------------------|------|

| Vdd                | Supply voltage                                                   | -0.3 to 4.8      | V    |

| Vin                | Input voltage on any control pin <sup>(1)</sup>                  | -0.3 to Vdd +0.3 | V    |

| T <sub>OP</sub>    | Operating temperature range                                      | -40 to +105      | °C   |

| T <sub>STG</sub>   | Storage temperature range                                        | -40 to +125      | °C   |

|                    | (HBM) ANSI/ESDA/JEDEC JS001                                      | ±2000            |      |

| ESD                | (MM) EIA/JESD22-A115                                             | ±200             | V    |

|                    | (CDM) JESD22-C101                                                | ±750             |      |

| ESD <sup>(2)</sup> | Per IEC61000-4-2, 150 pF, 330 $\Omega$ direct contact to housing | ±8000            | V    |

- 1. Supply voltage on any pin should never exceed 4.8V

- 2. Bypass capacitor of 200 nF or 1 μF (better) is highly recommended for ESD main clamp integrity.

This device is sensitive to mechanical shock, improper handling can cause permanent damage to the part.

This device is sensitive to electrostatic discharge (ESD), improper handling can cause permanent damage to the part.

DS13336 - Rev 4 page 7/15

## 4 Functionality

### 4.1 L/R channel selection

The L/R digital pad lets the user select the DOUT signal pattern as indicated in the following table. The L/R pin must be connected to Vdd or GND.

Table 7. L/R channel selection

| L/R | CLK low        | CLK high       |

|-----|----------------|----------------|

| GND | Data valid     | High impedance |

| Vdd | High impedance | Data valid     |

Note:

As the L/R pin is internally connected to GND via a 200  $k\Omega$  pull-down resistor, it is not mandatory to connect the pin itself to GND for the respective channel selection.

DS13336 - Rev 4 page 8/15

## Application recommendations

CODEC

Vdd

Clk

Dout

5

100 nF

5

1

2

L/R

BOTTOM VIEW

1 µF

Figure 9. MP23DB01HP electrical connections

Figure 10. MP23DB01HP electrical connections for stereo configuration

Power supply decoupling capacitors (100 nF ceramic, 1  $\mu$ F ceramic) should be placed as near as possible to pin 2 of the device (common design practice).

The L/R pin must be connected to Vdd or GND (refer to Table 7).

DS13336 - Rev 4 page 9/15

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

### 6.1 Soldering information

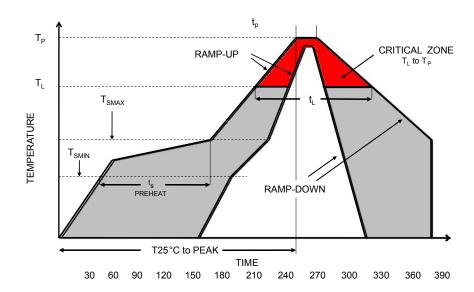

The RHLGA (3.5 x 2.65 x 0.98) mm package is also compliant with the RoHS and "Green" standards and is qualified for soldering heat resistance according to JEDEC J-STD-020.

Landing pattern and soldering recommendations are available at www.st.com.

Figure 11. Recommended soldering profile limits

Table 8. Recommended soldering profile limits

| Description                                    | Parameter                           | Pb free           |

|------------------------------------------------|-------------------------------------|-------------------|

| Average ramp rate                              | T <sub>L</sub> to T <sub>P</sub>    | 3 °C/sec max      |

| Preheat                                        |                                     |                   |

| Minimum temperature                            | T <sub>SMIN</sub>                   | 150 °C            |

| Maximum temperature                            | T <sub>SMAX</sub>                   | 200 °C            |

| Time (T <sub>SMIN</sub> to T <sub>SMAX</sub> ) | t <sub>S</sub>                      | 60 sec to 120 sec |

| Ramp-up rate                                   | T <sub>SMAX</sub> to T <sub>L</sub> |                   |

| Time maintained above liquidus temperature     | t <sub>L</sub>                      | 60 sec to 150 sec |

| Liquidus temperature                           | T <sub>L</sub>                      | 217 °C            |

| Peak temperature                               | T <sub>P</sub>                      | 260 °C max        |

| Time within 5 °C of actual peak temperature    |                                     | 20 sec to 40 sec  |

| Ramp-down rate                                 |                                     | 6 °C/sec max      |

| Time 25 °C (t25 °C) to peak temperature        |                                     | 8 minutes max     |

DS13336 - Rev 4 page 10/15

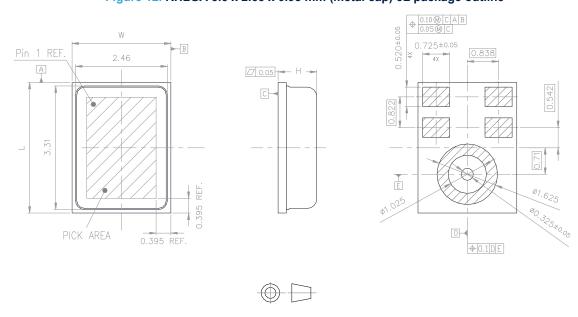

### 6.2 RHLGA-5L package information

Figure 12. RHLGA 3.5 x 2.65 x 0.98 mm (metal cap) 5L package outline

Dimensions are in millimeter unless otherwise specified General Tolerance is +/-0.15mm unless otherwise specified

### **OUTER DIMENSIONS**

| ITEM       | DIMENSION [mm] | TOLERANCE [mm] |

|------------|----------------|----------------|

| Length [L] | 3.5            | ±0.1           |

| Width [W]  | 2.65           | ±0.1           |

| Height [H] | 1.08 MAX       |                |

DM00368430\_3

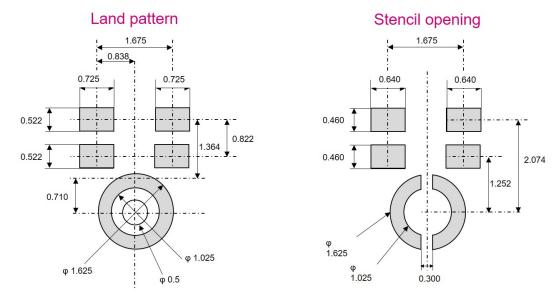

Figure 13. Land pattern and recommended stencil opening

DS13336 - Rev 4 page 11/15

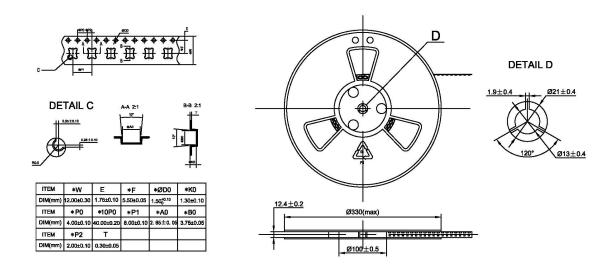

#### RHLGA-5L packing information 6.3

Figure 14. Carrier tape and reel mechanical specifications

Specifications: 1. Unmarked tolerance:  $\pm 0.1 \, \rm mm;$  2. Surface resistance:  $10^5-10^{12} \, \Omega/SQ,~25\pm5 \, C/50\pm5 \, \rm kRH;$

DS13336 - Rev 4 page 12/15

## **Revision history**

Table 9. Document revision history

| Date        | Version | Changes                                                                                                                                                                |

|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29-Apr-2020 | 1       | Initial release                                                                                                                                                        |

| 27-Jul-2020 | 2       | Added footnote 3 regarding the clock to Table 3: General microphone specifications                                                                                     |

| 10-Feb-2022 | 3       | Updated wake-up time in Table 2. Acoustic and electrical characteristics Replaced frequency response with Section 2.3 Typical performance curves Minor textual updates |

| 07-Mar-2022 | 4       | Updated Figure 3. Typical free-field response normalized to 1 kHz                                                                                                      |

DS13336 - Rev 4 page 13/15

## **Contents**

| 1   | Pin description |                                         |    |  |  |  |

|-----|-----------------|-----------------------------------------|----|--|--|--|

| 2   | Aco             | oustic and electrical specifications    | 3  |  |  |  |

|     | 2.1             | Acoustic and electrical characteristics | 3  |  |  |  |

|     | 2.2             | Timing characteristics                  |    |  |  |  |

|     | 2.3             | Typical performance curves              | 6  |  |  |  |

| 3   | Abs             | solute maximum ratings                  | 7  |  |  |  |

| 4   | Fun             | ctionality                              | 8  |  |  |  |

|     | 4.1             | L/R channel selection                   | 8  |  |  |  |

| 5   | App             | lication recommendations                | 9  |  |  |  |

| 6   | Pac             | kage information                        | 10 |  |  |  |

|     | 6.1             | Soldering information                   | 10 |  |  |  |

|     | 6.2             | RHLGA-5L package information            | 11 |  |  |  |

|     | 6.3             | RHLGA-5L packing information            | 12 |  |  |  |

| Rev | /ision          | history                                 | 13 |  |  |  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

DS13336 - Rev 4 page 15/15